Linuxsc Marchetti

Membros-

Posts Por Dia

0 -

Posts

6 -

Registrado em

-

Última visita

-

Créditos EBR

42 [ Doar ]

Informação Pessoal

-

Localidade

Penha/SC/Brasil

Últimos Visitantes

918 visualizações

Conquistas de Linuxsc Marchetti

Novato (1/14)

14

Joinhas

-

tutorial Modos de comunicação de SPI em Half-Duplex e Full-Duplex

Linuxsc Marchetti postou um tópico em Treinamento Eletrônica

Modos de Operação SPI comunicação são Full Duplex e Half Duplex. Modo Full Duplex SPI (comunicação simultânea): No modo full duplex, o dispositivo mestre SPI transmite dados simultaneamente para um escravo e recebe dados de um escravo. Desta forma, apenas um único dispositivo escravo pode ser acionado de uma só vez. Uma linha SS é usada para selecionar o dispositivo escravo SPI em particular. Usado as 4 linhas. Modo Half Duplex da SPI (leitura única): No modo mestre de leitura única duplex, o dispositivo mestre SPI recebe apenas dados de um escravo. Desta forma, apenas um único dispositivo escravo pode ser acionado de uma só vez. Uma linha SS é usada para selecionar o dispositivo escravo. Usado as 3 linhas. Modo Half Duplex SPI (Apenas Escrita): No modo de gravação única half duplex, o dispositivo mestre SPI só transmite dados para um escravo e não recebe nenhum dado do escravo. Desta forma, a operação simultânea com vários dispositivos escravos é possível. Usado as 3 linhas. Esses são dois tipos de operação de comunicação do SPI... Deixe sei Joinha, Obrigado...-

- spi

- comuinicação

- (mais 4)

-

Código de Erros... Erro -1: CPU da BaseBand ou saídas do PMU-IC de alimentação da BaseBand anormais. Erro 1: Problema na CPU da BaseBand ou saídas do PMU-IC de alimentação da banda base anormais. Erro 2: Problema na CPU da BaseBand ou saídas do PMU-IC de alimentação da BaseBand anormais. Erro 3: Existem atualmente dois tipos de relatórios de progresso para reparo desses erros: 1. Depois que o processo de restauração para perto de 2/3, o erro é causado pelo dano físico da CPU da BandaBase. 2. Restauração para 99% e apresenta o erro, o chip não pode ser completar o processo determinado, primeiro reparo, substituir o cristal oscilador de 24MHz. Erro 6 Restauração para em 2/3 na Nand, problema no Nand ou CPU. Erro 9: Nand Flash (disco rígido), verifique as tensões de alimentação da NAND, solda da NAND. Erro 10: Problema de autenticação do servidor! Iphone6 ??wifi ou CPU com falha de solda. CPU única mudança Iphone6 ?? Erro 11: Verifique se o pacote do firmware está completo, firmware corrompida. Erro 12: verificação de encerramento do firmware no processo de restauração. Erro 14: NAND, verifique a resistência ôhmica das trilhas entre a NAND (disco rígido) e a CPU, a tela azul é na maior parte desconectada do barramento de comunicação entre a CPU 5S Brush error 14 tela azul e apresenta desconexão da PCB ao software. Relatar mais de 15 problemas no disco rígido não exclui a fonte de alimentação do disco rígido. Erro 16: CPU de BandaBase para CPU, principalmente CPU. Erro 20: Reiniciando sempre em modo DFU Erro 21: Normalmente ligado a SDRAM, Nand, CPU e Bateria. Erro 23 8824 7.11 ou mais BaseBand, com provável curto-circuito causará 21 , 23 erros, por favor, remova a fonte de alimentação FL8 VVC após a restauração, o relatório de alta corrente da placa-mãe (PCB) erro 21, o circuito curto de BandaBase também será 21 e erro 23. Erro 26: Falha de comunicação entre CPU de BandaBase e Nand. Erro 27: Chip dados não correspondem, por favor use o chip de leitura e escrita instrumento para reparar o chip. Erro 28: CPU ou Nand Flash. Erro 29: Verifique o pino SWI de informação da Bateria, trilhas de SWI até mesmo Bateria. Ou problema de Rede. Erro 31: BaseBand. Erro 40: Nand Flash (disco rígido), verifique as tensões de alimentação da NAND. Erro 47: chip ou CPU de comunicação. Erro 48: CPU de BaseBand ou corrupção de Barramentos. Erro 50: Falha da CPU de BaseBand. Erro 53: Autenticação com o servidor de impressão digital ID de toque danificado. Erro 56: A maior parte destes erros estão ligados ao NFC, câmera traseira iphone6 ?? PMU câmera causando também erro 91. Erro 1003:Erro da BaseBand ou Nand Flash. Erro 1005: Nand Flash. Erro 1013: Erro normalmente relatado por problema de autenticação com o servidor de Atualização. Erro 1015: Normalmente é um problema com o firmware (downgrade), reparar o sistema do computador e depois efetuar a restauração novamente. Erro 1600: CPU APPLE. Erro 1601: CPU APPLE. Erro 1602: PMU, tristar (entrada de alimentação USB) ou problema no sistema. Erro 1611: Verificar trilhas, pads e soldas (REBALLING) da Nand. Erro 2002: Verifique se a conexão com o servidor Apple está relacionada ao uso de um servidor proxy. Erro 2003: Normalmente ligado a porta USB ou computador. Erro 2009: Substitua o computador, tente novamente depois de um tempo, a fonte de alimentação da NAND, tente efetuar a restauração várias vezes. Erro 3004: Bateria, cabo de dados não certificado, interface USB do computador é instável, utilizando HUB. Erro 3014: Verifique se o computador está conectado corretamente. Verifique se o backup SHSH do servidor está normal ao fazer o downgrade. Erro 3049: CPU APPLE. Erro 3194: O firmware não é compatível, 1: A verificação está desativada. 2: Demônio 3: Disparador 4: Periférico não está se comunicando. 5: Porta USB dianteira: use somente a traseira. 6: Cabo de Dados não certificado ou não original. 7: O firewall e anti-vírus do computador não está desligado. Erro 4005: Problema no disco rígido não exclui a fonte de alimentação do disco rígido, substitua o computador, tente em outro PC e reinicie a rede modem. Erro 4013: Sua tela reiniciar tem Inglês, barramento I2C bus com falha ou curto-circuito, chip controlador da camada inferior do CPU, NAND, Tristar/Hydra, Wi-Fi IC, etc. Erro 4014: CPU pode ser as linhas (barramentos de dados) da memória NAND, verificar pads, trilhas e raballing da NAND. Erro 4015: Normalmente ligado a SDRAM, camada superior da CPU. Erro 0xe800006B: O cabo USB está normal? Verifique se o dispositivo está conectado corretamente. Erro DXEXXXX Itunes não está instalado na unidade C. Erro -23: erro iPad6 -23 é a Bateria não presente. Não reconhecida caso esteja. Deixe seu Joinha, obrigado...

-

tutorial Abreviações das Leituras dos esquemas elétricos da Apple.

Linuxsc Marchetti postou um tópico em Treinamento Celulares

Abreviações Apple AP= APPLE PROCESSOR, processador de Aplicação da Apple ex: A11. ANODE=Terminal POSITIVO. AP_TO_PMU_WDOG_RESET= Apple processor para o power manager watch dog e reset telecélula. AP_TO_BBPMU_WDOG_RESET=Apple processor para o power manager da BaseBand sinal de watchdog e reset. ALS= Sensor de Luminosidade. ALIVE= Informação de Bloco VIVO, circuito em funcionamento. AMPLIFIER= Amplificador. AMUX = Analógico Multiplex ACESSORY=Acessório. ACTIVE= Ativar. ADC= Analogic Digital Converter, conversor de sinal Analógico. ANT= Antena. ATTENTION= Atenção. BATT= Bateria. BB= Base Band. BIAS= Polarização, inclinação. BI=Battery Infomation, informação do tipo de Bateria. BL= BACK LIGHT luz de fundo do módulo LCM (display). BUS= Barramento de dados. BUF= BUFFER. BUCK= CONVERSOR DE TENSÃO conversores Buck, converte tensão contínua em em outra tensão contínua. BUCK FB= Buck FieldBack, retorno de informação da tensão regulada. BUCK LX= Saída de tensão dos conversores Buck internos do PM. BOARD= Placa de circuito impresso. BOOST= Conversor elevador de tensão. BOOTSTRAPPING= Parte do hardware e software que cuidam da energização inicial, primária até transferir o controle para a CPU. BOTTOM= Lado inferior da placa de circuito impresso. BUTON= Botão, chave. CATODO= Terminal Negativo. CAM=Câmera. CAM_PMU= Regulador de Tensão da Câmera. CAT= CATODO Terminal NEGATIVO. CHATODE= CATODO Terminal NEGATIVO. CHARGER= CARREGADOR. CERM= CAPACITOR CERÂMICO. CLK = CLOCK, sinal de clock. CPU= UNIDADE PRINCIPAL DE PROCESSAMENTO. CLK OUT= Saída de pulso de clock. CERM= Capacitor Cerâmico. CTS= PORTA VISRTUAL. CLK32K= Clock de 32KHz. CLKOUT= Saída de sinal de Clock. COMPASS= Bússola CONN= Conector, terminal do conector FPC. CONNECT=Conectado, conexão. CODEC=Codificador de Sinais Digitais. COOL= linha fria, informação de temperatura. CRITICAL= Componente crítico no circuito. DATA= Dados Digiais. DATA_P= Dados Digitais Positivo. DATA_N= Dados Digitais Negativo. DDR = Double Data Rate, capacidade das memórias de transmitir dados duas vezes por ciclo. DETECT= Detector de sinal. DISABLE= Desabilitar. DIODE= Diodo. DISP= Display. DESACTIVE= Desativar. DRIVER= Circuito acionador final de uma carga. DOUT= Saída de sinal Digital. DOCK= Conector de Dados/Carga. E75 dock 30 pinos e ligthining. EMMC= Controle de memória multimídia embarcada. EN= Enable, habilitar, ligar. EXT=Externo EXT_REF_CLK_P= Clock de referência externo positivo. EXT_REF_CLK_N= Clock de referência externo negativo. E75= Cabo de dados Lightining. FCAM=Câmera Frontal. FIXED= Fixo. FD = Ponto de teste na Placa PCB. FORCE= Forçar. FRONTMIC3= Microfone Frontal 3. FILT=Filtro. FLIT_P= Filtro Positivo. FILT_N=Filtro Negativo. FLEX CONNECTOR= Conector do Cabo Flex. FPC= Flex Print Circuit, Conector do flex cable da placa. GPU= Processador Gráfico. GNSS=GLONASS GG= Gas Gauge, sensor de nível de carga da Bateria. GND= Ground, terminal ligado ao negativo da alimentação. CPIO= General Purpose Input/Output são basicamente portas programáveis de entrada e saída de dados. ISP= IN CIRCUIT PROGRAM, barramento para regravação da MCU no circuito. IN=Input, Entrada. INT= Inicialização. IO= Entrada e Saída. I2C TIPO Barramento de Comunicação. JTAG= Join Test Action Group, protocolo de regravação de software. LCM= Modulo Cristal Líquido, display lcd. L= Pulso alto para baixo, ativa em nível baixo. LED= Diodo Emissor de Luz; LOWERMIC=Microfone inferior. LOWER ANT= Antena Inferior. LDO= Load, saída de corrente do PM ou regulador de tensão. NC= NAO CONECTADO, NAO EXISTE. MAX= Valor máximo. MAIN_MIC=Microfone Principal. MLB=Mobile Board, placa do iPhone. MIC=Microfone. MIPI=Barramento de Dados Digitais de Alta Velocidade. MUX= Multiplexador. MF= Resistor Metal Film. N= Negativo. NC= Não montado, não presente na placa, não conectado. NFC= Near Fild Comunications, protocolo de comunicação por proximidade. NTC= Resistor sensível a variação de temperatura, coeficiente negativo. NOSTUFF= não montado. NOISE MIC= Microfone de Ruído. Hold_Reset= Segure para resetar. H= Pulso Baixo para Alto, ativa em nível Alto. OVP= TENSÃO DE SAÍDA POSITIVO. OUT= SAÍDA. P=Positivo. PP=Power Positivo, linha de alimentação. PCB= Print Circuito Board, placa de circuito impresso. PCIE= Padrão de Comunicação. PMU= POWER MANAGER UNIT. PWR=Power. PM=Power Manager, Gerenciador de Energia. PMU_TO_FORCE_DFU= Forcar a entrada no modo DFU. PP= POWER POSITIVE= Tensão de alimentação. POWER SUPPLIES= Fornecimento de Tensões de alimentação; PP_VDD_MAIN= Tensão positiva Principal do Circuito. POWER KEY= Chave Power, tecla power. PROX= Próximo, proximidade. PULL DOW= Mantem tensão nível baixo na entrada do microprocessador, feito por resistores ligados ao negativo GND. PULL UP= Mantem tensão nível alto na entrada do microprocessador, feito por resistores ligados ao VCC. PLL=Elo Travado por Fase. REF= Sinal de Referência. REF CLOCK_P= Clock de referência positivo. REF CLOCK_N= Clock de referência negativo. RF= Rádio Frequência. REARMIC= Microfone Superior. REG= Tensão Regulada. REG_ON= Tensão Regulada Ativada. RST= Reset, recomeçar. RESREF= Reset de referência. VER= REVISÃO RINGER= Campainha. RSV= Receiver, recebendo comando ou sinal. RAM=Câmera Traseira. RX= Recepção. RX_P= RX Positivo. RX_N=RX Negativo. RXD=Received Exchange Data, recebe dados de uma fonte para outra. ROOM= Sala onde se encontram os componentes. SYSTEM= Sistema. SYM= Sistema. SYNC= Sincronismo. SLEEP=Clock de Espera, mode de espera. SW= Chaveador para elevar a Tensão do conversor booster. SPI = Serial Peripheral Interface ou SPI é um protocolo que permite a comunicação do microcontrolador com diversos outros componentes, formando uma rede. SHUTDOWN= Desligamento. SCK = Serial ClocK. SDA = Serial Data (DADOS EFETIVOS). SCL= Serial Clock (TEMPORIZA O DISPOSITIVO). SDRAM) é uma memória de acesso dinâmico randômico (DRAM) que é sincronizada com o barramento do sistema. SDRAM passaram a ser chamadas de "SDR", ou "Single Data Rate". STB= Em espera, stand by. SEL= Seleção. Selecionar. SENSE= Sensor. SOC = System on Chip, processador com construção em wafers, camada sobre camada. SPEAKER= ALTO FALANTE. SPKAMP2= Amplificador de campainha 2. SRAM= SLAVE RAM. SW= Chave, chaveado, chaveador. STROBE= Led Flash. SOLENOID= Motor Vibra Call Taptic Engine; TEST MODE= Modo de Teste. TELE CLK= Aproximação para Câmera. TP= Test Point, ponto de teste. TOP= Lado superior da placa de circuito impresso. TP= Test Point , ponto de teste na placa. TX=Transmissão. TX_P=Sinal de Transmissão Positivo. TX_N=Sinal de Transmissão Negativo. TXD= Transmite Exchange Data, transmite dados de uma fonte para outra. UART= Unidade Receptora e Transmissora assíncrona Universal. USB_DATA= Dados USB D+ ou D- USB_ID= Identificação de Cabo USB conectado. USB_VBUS= Tensão de entrada 5VDC USB. UPER ANT= Atena Superior. VDD, VCC= Fornecimento de Tensão positiva. VAR= Variável. VBATT_SENSE= Sensor de Tensão da Bateria. VBAT_VCC= Tensão positiva da Bateria.VCC MAIN = Malha principal para prover as outras tensões das malhas seguintes. VSS= Ground, zero terminal negativo. VBUS= Tensão de trafego de dados. VBUS1_VALID = Tensão 5volts USB válida. VREG= Tensão Regulada. VOL= Volume. VSENSE= Tensão do Sensor, sensível a variação de Tensão; WDOG= Watch Dog pulso de cão de guarda do sistema processado. XTAL= Cristal Oscilador, clock gera o ciclo de máquina para o processamento. XTAL_AP_24M_IN Entrada de clock do AP com frequência de 24 MHZ. XTAL_AP_24M_OUT Saída de clock do AP com frequência de 24 MHZ. WAKE= Despertar, ligar, acordar. WAKEUP= Ligar, despertar. WARM= Quente, sensor de temperatura, informação de temperatura. Se quiserem ajudarem acrescentar mais abreviações, fiquem a vontade! Não esqueça de dar seu joinha!- 4 respostas

-

- 12

-

-

-

- abreviações

- apple

-

(mais 1)

Tags:

-

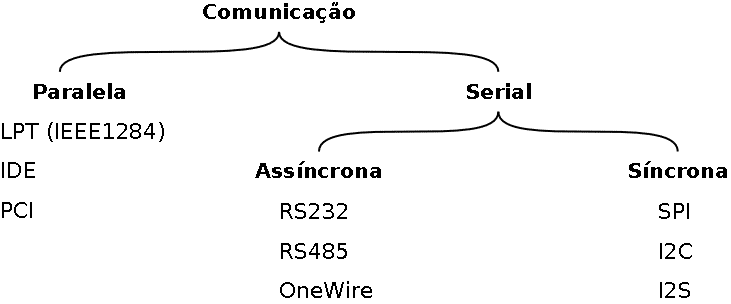

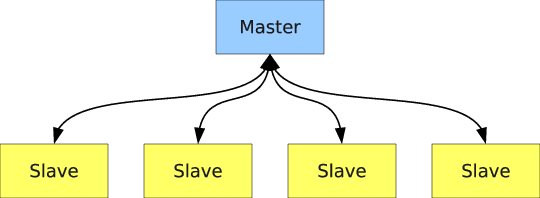

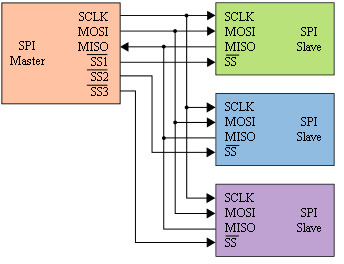

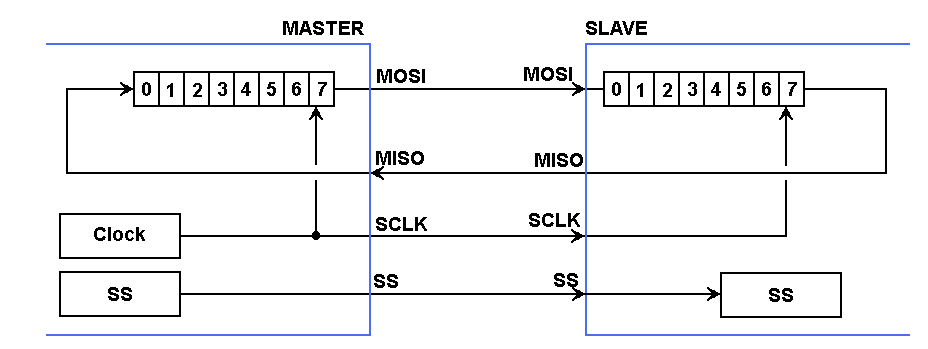

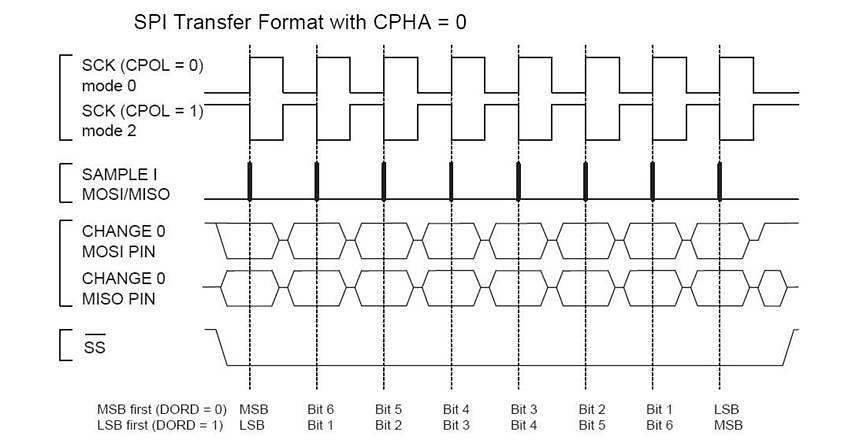

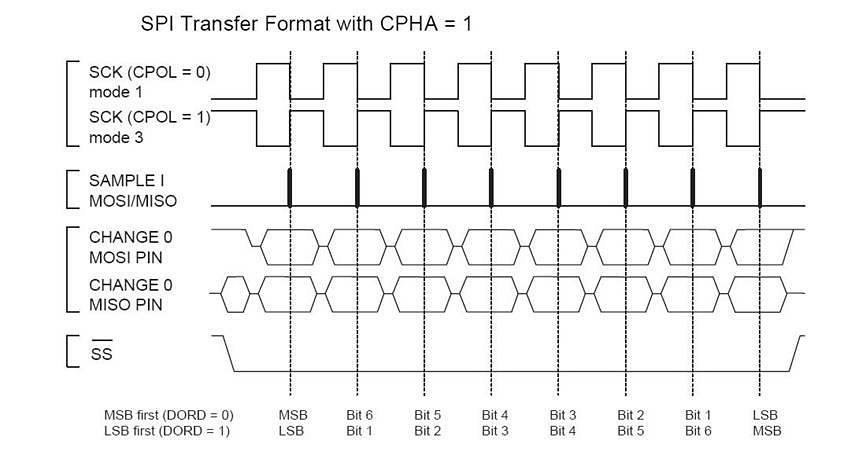

O objetivo deste artigo é definir os princípios da comunicação SPI, quais são suas vantagens e onde esses dispositivos são utilizados. Também vamos analisar os fundamentos básicos de hardware. Tipos de Comunicação Serial Uma vez que os equipamentos eletrônicos vêm agregando mais e mais funções, a utilização de diversos circuitos integrados torna-se cada vez mais comum. No entanto, não é mais possível estender longos barramentos de comunicação paralelos, pois tornariam as placas de circuito impresso caras e muito grandes. Logo, uma comunicação serial entre esses dispositivos se torna necessária. Diversas tecnologias de interligação serial entre dispositivos foram desenvolvidas, podendo ser separadas em duas grandes categorias, a comunicação síncrona e a comunicação assíncrona. Dentre os métodos de comunicações mais conhecidos, destacam-se três: UART: Universal Asynchronous Receiver Transmitter; SPI: Serial Peripheral Interface; I2C: Inter Integrated Circuit. Já estamos bastante familiarizados com a comunicação serial assíncrona pelo uso do padrão UART (RS232). No entanto, existem grandes vantagens no uso de uma comunicação serial síncrona em detrimento da assíncrona. Além disso, há grandes diferenças mesmo entre os protocolos síncronos. Apesar do padrão de cada protocolo definir limites máximos de taxas, cada fabricante possui a liberdade de desenvolver dispositivos com suas velocidades. Abaixo temos um comparativo entre diversos padrões dispositivos seriais: Como um exemplo de que esses limites podem ser ultrapassados, temos AT45BD0100D da Adesto. Essa memória SPI pode chegar até 66MHz (66Mbps) de taxa de transferência. Para o I2C, o 24FC64 da Microchip pode chegar a 1MHz (1Mbps). Na comunicação serial síncrona definimos também o conceito de Mestre-Escravo. Normalmente o gerador do sinal de sincronismo é definido como o Mestre (Master) da comunicação. Para os dispositivos que utilizam do sinal de sincronismo gerado damos a definição de Escravo (Slave). A ligação mais comum desse tipo de comunicação é um Master e vários Slaves. Comunicação SPI A comunicação SPI possui algumas características básicas. Primeiramente os sinais de comunicação possuem uma direção fixa e definida. Isso significa que sempre existem dois transistores definindo o estado de um pino (Push-Pull). Essa característica é uma das grandes diferenças entre outras comunicações seriais como I2C e OneWire, que possuem um mesmo barramento de dados para os sinais de entrada e saída através do esquema de dreno-aberto (Pull-Up). Apesar de utilizar dois sinais de comunicação de dados em vez de um, é possível atingir velocidades maiores de comunicação. Isso porque há pouca deformação do sinal. Outra característica é que toda troca de dados acontece sempre em ambas as direções. Em outras palavras, cada bit trocado entre o Master e um Slave trás um bit do Slave para o Master. Dessa forma, definimos que a comunicação é sempre full-duplex. Os pinos básicos de comunicação entre dispositivos SPI e o esquema padrão de ligação são dados conforme abaixo: O sinal de SS funciona como Seleção de Escravo (Slave Select). É um sinal ativo em nível baixo, o que significa que o dispositivo é selecionado quando este pino se encontra em nível baixo. No entanto, muitos dispositivos utilizam este sinal como sincronismo de frame. Dessa forma, é um sinal importante que deve ser respeitado. O Dispositivo O princípio básico de um dispositivo SPI é o Shift-Register. Esse tipo de dispositivo faz a conversão de um registrador paralelo para sinais seriais de acordo com clock. Cada borda recebida no terminal de clock do dispositivo significa um bit transferido. Da mesma forma esse tipo de dispositivo é capaz de receber dados vindos de maneira serial e convertê-los para um valor em um registrador paralelo. A SPI não apenas é capaz de fazer essa conversão serial/paralelo, como também possui o gerador de clock, o controle para a troca do frame e o slave-select. Dessa forma, tornando ele um dispositivo de comunicação completo. Na figura abaixo podemos observar como ele se dispõe. Forma de Onda Por padrão a comunicação SPI permite a configuração das bordas de comunicação do clock através de sua polaridade e fase. A configuração da polaridade se dá através de CPOL (Clock Polarity), e a configuração da fase se dá através de CPHA (Clock Phase). Seus modos possíveis são: Outra característica fundamental na comunicação é a definição da posição do bit mais significativo (MSB). Através de DORD é possível definir que o bit mais significativo será o primeiro (DORD = 0) ou o último (DORD = 1) bit trocado. É possível observar todas essas características através das duas imagens abaixo: Conclusão Pudemos observar as principais características da comunicação SPI, além de um comparativo de hardware com outros tipos de comunicação. Observamos diagramas do funcionamento do dispositivo e entendemos como se dá a forma de onda. Não esqueça de dar um Joinha! Escrito por: Francesco Sacco. https://www.embarcados.com.br/

-

tutorial I3C, o futuro substituto dos barramentos I2C e SPI?

Linuxsc Marchetti postou um tópico em Treinamento Eletrônica

Atualmente, os barramentos I2C e SPI são os mais utilizados para conectar dispositivos externos (sensores, EEPROM, etc) a microcontroladores e SoCs. Mas a vida útil deles pode estar no fim, porque vem aí o barramento I3C. O I2C é um barramento bem antigo, criado em 1982 pela Philips Semiconductor, com mais de 35 anos de vida! É um barramento simples, com apenas duas linhas de comunicação: clock (SCL) e dado (SDA). Esta simplicidade facilita o projeto da placa de circuito impresso, mas traz algumas desvantagens. O endereçamento é feito no protocolo, sendo tipicamente limitado a 7 bits, o que permite um máximo de 127 dispositivos conectados ao barramento. Outra grande desvantagem do barramento I2C é a velocidade de comunicação, tipicamente de 100Kbit/s a 400Kbit/s. O barramento SPI também é bastante antigo, criado em meados da década de 80 pela Motorola. Sua arquitetura é mais complexa, exigindo 4 linhas de comunicação: clock (SCLK), master output (MOSI), slave output (MISO) e slave select (SS). Comparado ao I2C, sua grande desvantagem é a complexidade do projeto da placa de circuito impresso, principalmente se você tiver mais de um dispositivo SPI conectado ao barramento, o que vai exigir pinos extras de I/O para fazer a seleção do slave (chip select). Mas a velocidade de comunicação é muito maior, podendo chegar a 60Mbit/s, dependendo do clock da CPU e do dispositivo. O barramento SPI também consome menos energia que o barramento I2C. Qual o problema destes barramentos? Nenhum. A questão é que eles se complementam, cada um resolvendo um domínio de problemas diferentes. O I2C é mais simples, porém mais lento. O SPI é mais rápido e consome menos energia, porém pode aumentar bastante a complexidade do projeto de hardware. Além disso, ambos os barramentos I2C e SPI não suportam interrupções. Isso significa que será necessário o uso de pinos extras de I/O para receber interrupções de dispositivos conectados a estes barramentos. O mesmo vale para gerenciamento de energia. Não existe nenhum suporte nestes barramentos para colocar um dispositivo em modo de baixo consumo, e normalmente a implementação de gerenciamento de energia é feita por fora, via algum registrador do dispositivo ou pino extra de I/O. E se eu disser à vocês que o barramento I3C tem tudo isso e muito mais? :-) O I3C é um padrão de barramento criado pela MIPI Alliance, a mesma responsável por outros barramentos bastante comuns como o CSI (Camera Serial Interface) para câmeras. O nome I3C vem de Improved Inter Integrated Circuit, e seu desenvolvimento começou em meados de 2014. A primeira versão da especificação foi lançada no começo de 2017, e em dezembro de 2017 o padrão foi aberto ao público, o que deve incentivar seu uso no projeto de novos circuitos integrados. O I3C traz o melhor dos mundos I2C e SPI. É simples, e assim como o I2C, utiliza apenas duas linhas de comunicação: clock (SCL) e dado (SDA). Mas é muito mais rápido que o I2C, com velocidades comparáveis ao SPI, começando em 10Mbit/s e podendo passar de 30Mbit/s! O I3C possui suporte à interrupção integrado ao barramento de comunicação (In-Band Interrupt). Ou seja, você não precisa de pinos extras de I/O para receber uma requisição de interrupção de um dispositivo I3C. O mesmo acontece com gerenciamento de energia. Já existe suporte integrado no barramento para gerenciamento de energia e modos de baixo consumo de dispositivos I3C. O endereçamento dos slaves é dinâmico. Isso significa que, durante a inicialização do barramento, o master atribui dinamicamente endereços aos slaves conectados ao barramento. Além disso, cada dispositivo I3C possui um número identificador de 48 bits chamado Provisional ID, que contém informações sobre o dispositivo, incluindo o fabricante e o part number. Desta forma, o master consegue identificar (enumerar) em tempo de execução os dispositivos conectados ao barramento. Ou seja, não será necessário declarar dispositivos I3C no device tree! O barramento I3C é hotplug (eles chamaram esta funcionalidade de hot-join). Ou seja, você pode conectar um dispositivo no barramento I3C dinamicamente, em tempo de execução. Além disso tudo, o I3C é compatível com o I2C. Isso significa que, se foram tomados alguns cuidados com o projeto da placa de circuito impresso, dispositivos I2C irão funcionar em um barramento I3C! Tem uma tabela bem bacana disponível na documentação que resume o funcionamento do barramento, diferenciando o I3C, I2C e SPI (clique na tabela para abrir uma versão de melhor resolução): Por falar em documentação, este Whitepaper resume as características do barramento, existe um FAQ de leitura rápida que pode tirar muitas dúvidas sobre seu funcionamento, além claro da especificação completa que pode ser baixada no site da MIPI Alliance. Ainda não existem dispositivos compatíveis com I3C, mas o kernel Linux está em vias de suportá-lo com a segunda revisão dos patches enviada recentemente pelo Boris Brezillon, e atualmente existem algumas implementações de IP do I3C, como este da Silvaco e este da Cadence. A especificação do I3C foi desenvolvida pelo MIPI Sensor Working Group da MIPI Alliance, que possui entre seus membros empresas gigantes como AMD, Broadcom, Google, Cadence, Intel, Lattice, MediaTek, Mentor Graphics, Nvidia, NXP, Qualcomm, Sony, STMicroelectronics, etc. Não dá para negar a força destas empresas no mercado de tecnologia e semicondutores, e somando a isso o fato do padrão ser aberto ao público e não ter nenhum tipo de royalties associado, é bem provável que a partir de 2018 comecem a aparecer dispositivos, microcontroladores e SoCs compatíveis com este barramento. Quem viver, verá! Não esqueça de dar um joinha! Um abraço... Conteúdo escrito por https://sergioprado.org/i3c-o-futuro-substituto-dos-barramentos-i2c-e-spi/ Sergio Prado-

- 2

-

-

-

- protocolo de comunicação

- i2c

- (mais 3)

-

apresentação Boa tarde a todos novos amigos dessa caminhada!

Linuxsc Marchetti postou um tópico em Apresentações

Rafael / Penha / SC Conheço anos a eletronicaBR, meu primeiro contato foi do conhecimento através do google. Nível técnico, estudante. Faculdade de Engenharia. Especialista em reparo apple. Trabalho como técnico em eletrônica mais de 6 anos, especialista em reparos em apple, aqui não procuro apenas a fim de smartphone, mas sempre evoluindo com qualquer conteúdo sendo eletrônica... Estou aqui para compartilhar meus conhecimentos e espero aprender bastante com essa comunidade...

SOBRE O ELETRÔNICABR

Técnico sem o EletrônicaBR não é um técnico completo! Leia Mais...