malek

Membros-

Posts Por Dia

0.01 -

Posts

24 -

Registrado em

-

Última visita

-

Créditos EBR

61 [ Doar ]

Informação Pessoal

-

Sexo

Male

-

Localidade

egypt

Últimos Visitantes

O bloco dos últimos visitantes está desativado e não está sendo visualizado por outros usuários.

Conquistas de malek

Novato (1/14)

6

Joinhas

-

@Leonildo

-

@Jesiel obrigado mano

-

@Jesiel Irmão, a questão aqui é como posso determinar se o sinal passa ou não pelo diodo ou não

-

NINGUÉM PODE ME AJUDAR

-

eu adiciono outro diodo não SCHOTTKY ele está trabalhando com a mesma idéia

-

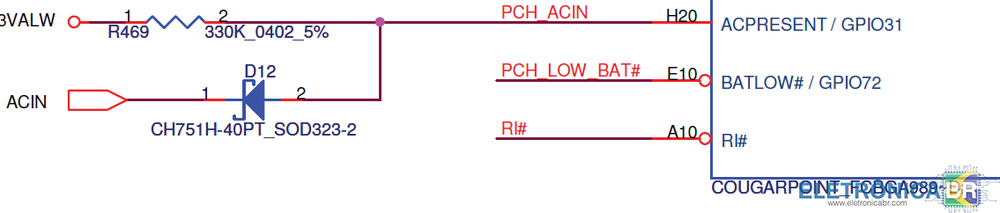

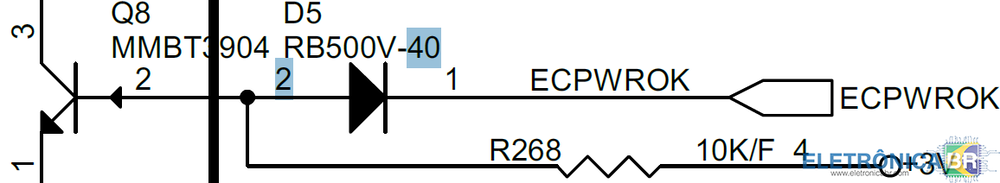

Tenho uma consulta e não consigo entender a ideia de trabalhar com um diodo em muitos planos Sabe-se que o diodo trabalha em uma direção, do lado positivo para o negativo, para que a corrente passe e, se o sinal ou a corrente vier do lado negativo, ele não passará Um exemplo disso Às vezes acho que o sinal está chegando no diodo na direção negativa, não sei como passar para o outro lado E eu quero entender como isso é feito

-

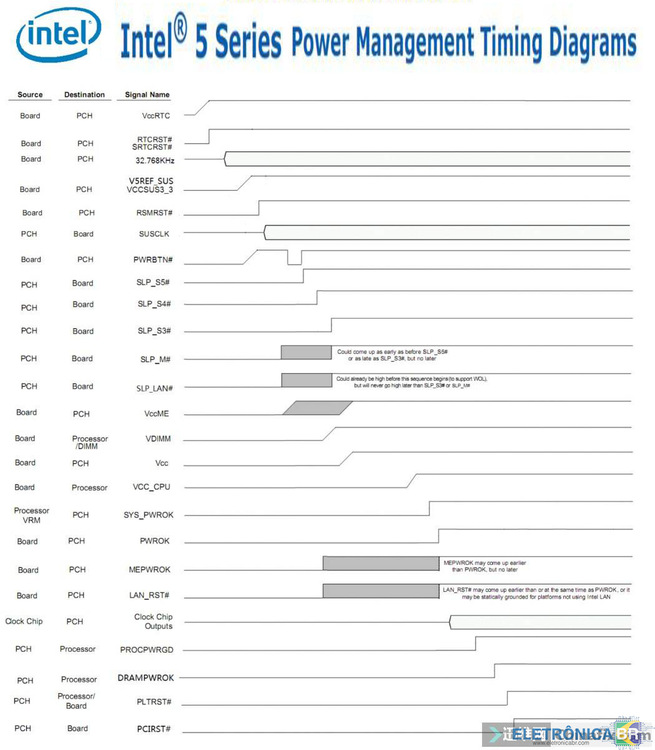

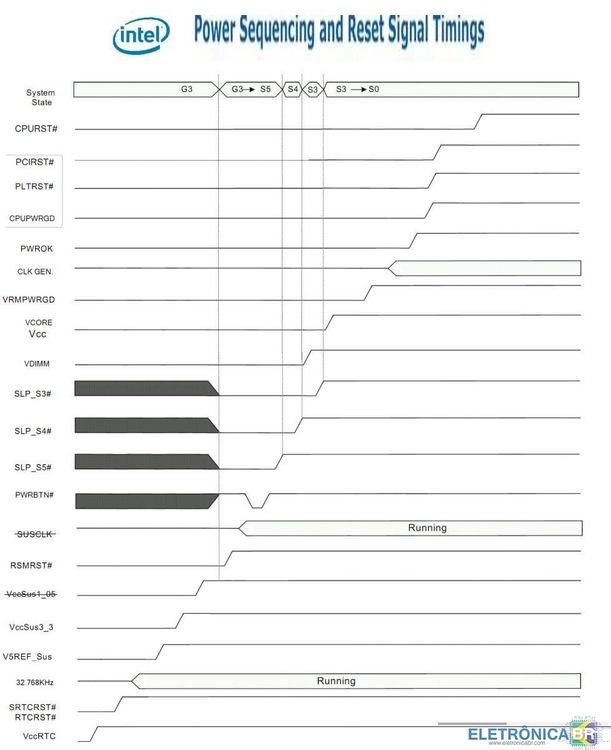

Explicação da hora padrão da série Intel 5 Interpretação do sinal: O VCCRTC fornece energia de 3V da placa principal à ponte e alimenta o circuito RTC da ponte para salvar os parâmetros COMS RTCRST # / SRTCRST # para a ponte da placa-mãe com até 3V de altura, o circuito de sinal de reinicialização RTC 32.768kHz crystal perto de 32.768kHz ponte, a ponte alimenta o cristal e o cristal fornece a frequência para a ponte INTVRMEN é usado para conectar o regulador que gera uma tensão de espera de 1,05V dentro da ponte VCCSUS3_3 input à fonte de alimentação à espera da ponte de 3.3V RSMRST # O alto nível de 3.3V recebido pela ponte significa informar à ponte que a tensão de espera está OK 32.768kHz relógio do SUSCLK PCH. Se o EC tiver um oscilador de cristal embutido, o SUSCLK geralmente será enviado ao EC, e o relógio síncrono terá pouco efeito e poderá ser ignorado. PWRBTN # O sinal de disparo de borda descendente recebido pela ponte, 3.3V-0-3.3V, informa que a ponte pode ser conectada Após a ponte SLP_S5 # receber PWRBTN #, defina SLP_S5 # para 3.3V para sair do estado de desligamento SLP_S4 # PCH envia SLP_S4 # 3.3V para sair do estado de suspensão SLP_S3 # PCH envia SLP_S3 # 3.3V para sair do estado de suspensão e entrar no estado de inicialização S0 SLP_M # emitida pela ponte aberta para o módulo ME (gerenciamento de motor equipado com Intel integrado na ponte norte) Se a placa-mãe suportar AMT (Active Management Technology) e abrir o AMT quando a função, esse sinal será gerado antes da viagem, o AMT será fechado Quando a função, o tempo deste sinal é consistente com SLP_S3 #, se a placa-mãe não suportar AMT SLP_M # não for usado no ar SLP_LAN # O sinal original de controle da fonte de alimentação da placa de rede Intel, exceto o ThinkPad, basicamente não usa esse sinal flutuante, pode ser ignorado A fonte de alimentação do módulo VCCME ME é controlada pelo SLP_M # quando a placa-mãe não suporta AMT, SLP_M # está flutuando e o VCCME usa diretamente a fonte S0, como a fonte de alimentação do barramento VCC3_3 VDIMM refere-se à fonte de alimentação da memória VCC refere-se à fonte de alimentação da ponte, à fonte de alimentação do módulo de memória da CPU VDDQ, à fonte de alimentação do barramento, à fonte de alimentação do circuito com bloqueio de fase VCCPL, à fonte de alimentação do monitor conjunto VAXG, etc. VCC_CPU Fonte de alimentação do núcleo da CPU SYS_PWROK pela ponte do chip de gerenciamento de energia da CPU emitido 3.3V de alta,. Sequência de tempo 4 chipset VRMPWRGD anteriormente PWROK A PCH recebe um nível alto de 3,3V, indicando que a tensão no estado S0 está OK (fonte de alimentação de ponte e barramento) MEPWROK A fonte de alimentação do módulo ME está boa. 3.3V não suporta AMT, MEPWROK e PWROK juntos LAN_RST bom sinal de energia da placa de rede, se não a placa de rede Intel integrada, esse sinal será forçado a TERRESTRE Clock Chip Outputs O chip do relógio é ativado e gera cada grupo de relógios O PG enviado pela ponte PROCPWRGD para a CPU indica que a tensão do núcleo da CPU é 1,05V CPUPWRGD quando o chipset é anterior a 4 séries DRAMPWROK A PCH envia ao módulo de memória para a CPU uma boa fonte de alimentação, a PCH possui uma saída de dreno aberta e um pull-up externo de 1,1V A redefinição da plataforma emitida pelo PLTRST # PCH redefine 3,3V para cada slot de chip e é convertida (geralmente 1,1V em série) conforme a redefinição da CPU RSTIN # A redefinição do PCI emitida pelo PCIRST # PCH não é usada em todos os notebooks de 3.3V e pode ser ignorada próximo tópico explicarei o tempo padrão (CPU de 2 e 3 gerações)

-

Explicação de tempo padrão da série Intel 4 G3: Toda a energia do sistema está desligada S5: Estado desligado S4 Estado de hibernação S4 Estado de suspensão S0: estado ativado Interpretação do sinal: VCCRTC: Fonte de alimentação para o circuito RTC South Bridge, 3V, para alimentar o chip CMOS (RAM) dentro da South Bridge. RTCRST #: o sinal de redefinição do circuito RTC South Bridge. Após 3V ICH9, um sinal de redefinição RTC foi adicionado, o nome é SRTCRST # 32.768kHz: Depois que o Southbridge obtém VCCRTC e RTCRST #, ele fornece energia ao cristal, o cristal começa a vibrar e a tensão entre os dois pinos do cristal fica entre 0,1 e 0,5V INTVRMEN: um regulador que gera tensão de espera de 1,5V dentro da ponte V5REF_SUS: tensão de espera de 5V VCCSUS3_3: tensão de espera de 3.3V VCCSUS1_05: Southbridge interno para gerar sua própria fonte de alimentação 1.05V, não controla RSMRST # informa Southbridge que a tensão de espera de 3.3V é normal e 3.3V é controlada por circuito externo O relógio de 32K emitido pelo SUSCLK South Bridge após o recebimento do RSMRST #. A maioria das máquinas antigas não usa. Pode ser ignorado. Novas máquinas são enviadas para a EC . PWRBTN # Botão POWER BOTÃO POWER, sinal de pulso 3.3V-0-3.3V, gatilho de queda de borda SLP_S5 # 3.3V sinal de controle de saída da ponte sul SLP_S4 # 3.3V sinal de controle de saída da ponte sul (geralmente apenas um S5 # e S4 # é usado para gerar energia na memória) SLP_S3 # 3.3V sinal de controle da ponte sul para sair do estado de suspensão (geralmente usado para controlar a fonte de alimentação da ponte, a fonte de alimentação do barramento, a fonte de alimentação de exibição independente, etc.) Potência de memória VDIMM VCC / VCORE refere-se à fonte de alimentação em ponte (3.3V 5V 1.5V), fonte de alimentação em barramento (1.05V), fonte de alimentação de exibição independente, fonte de alimentação da CPU e outra fonte de alimentação S0 VRMPWRGD informa Southbridge que a potência da CPU está normal no momento 3.3V O chip de relógio CLK GEN começa a funcionar, enviando vários relógios A PWROK informa a Southbridge que a fonte de alimentação está normal no momento (tarefa SLP_S3 # concluída) CPUPWRGD Southbridge emitido para a CPU do PG 1.05V PLTRST # Redefinição da plataforma A primeira redefinição emitida pela South Bridge, geralmente para o chip onboard (North Bridge EC, etc.) PCIRST # O segundo reset emitido pela ponte sul de reset PCI geralmente é de 3,3V para o mini slot. Após o CPURST # Northbridge receber o PLTRST #, ele envia uma redefinição de 1,05V para a CPU

-

@Leonildo você poderia me ajudar eu preciso vincular este curso

-

-laptop-power-sequence-training/

malek respondeu o tópico de Vijay Arockia Raj Vijay em Treinamento Notebooks

me desculpe, eu sou um estrangeiro, eu não quero dizer isso -

estou procurando curso de conserto de portátil em inglês foi www.mega.nz o administrador foi português estava nesta seção https://eletronicabr.com/forums/forum/34-treinamento-notebooks/

-

link error

-

malek começou a seguir: Samsung NP270E5E BA92-12068B BA41-02206A Boardview

-

boardview Samsung NP270E5E BA92-12068B BA41-02206A Boardview

malek respondeu o tópico de maxima em Gerenciador de arquivos

good- 7 respostas

-

- samsung np270e5e

- ba92-12068b

- (mais 1)

-

bios BIOS HP- Placa 6050a2555201-mb-a02 18703.rar

malek respondeu o tópico de ian.nakano em Gerenciador de arquivos

good

SOBRE O ELETRÔNICABR

Técnico sem o EletrônicaBR não é um técnico completo! Leia Mais...